-

-

September 24, 2023 at 10:25 am

ty_jpn

SubscriberDear everyone

Hi,The following script was created to determine the fringe capacitance of parallel plate electrodes in MAPDL.

---------------------------------

do,i,0,100,10 !変数,初値,終値,増幅度(ループの始まり)fini/cle/vie,1,1,1,1/sys,del file*.png/PREP7C*** Plate dimensions (um scale)eps0=8.854e-12 ! FREE SPACE PERMITTIVITYwidth = (100*1e-6) + (i*1e-6)height = 20*1e-6thickness = 3*1e-6separation = 10*1e-6d_dmn = 10*1e-6 ! DEPTH SURROUNDING DOMAIN EXTENDS BEYOND ELECTRODESd_inf = 5*1e-6 ! DEPTH OF INFINITE BOUNDARY ELEMENT MESHesz = 3*1e-6 ! MESH SIZEV = 0.01 ! APPLIED VOLTAGEC*** Configured for electrostatic analysis of 3D 8-node elementsET,1,SOLID123C*** Define infinite elementET,2,111,2,1C*** Material properties (relative dielectric constant in vacuum)!MP,PERX,1,8.854e-12 ! THIS IS ABSOLUTE PERMITTIVITY IN MKS, WHICH WORKS OK, BUT...MP,PERX,1,1 ! WE GENERALLY USE RELATIVE PERMITTIVITY INSTEADC*** Create your first plateBLOCK,0,width,0,height,0,-thicknesscm,electrode1_a,areaC*** Create second plateasel,noneBLOCK,0,width,0,height,separation,separation+thicknesscm,electrode2_a,areaC*** SURROUNDING DOMAINallscm,scrap1_v,volu*get,xmin,kp,,mnloc,x*get,xmax,kp,,mxloc,x*get,ymin,kp,,mnloc,y*get,ymax,kp,,mxloc,y*get,zmin,kp,,mnloc,z*get,zmax,kp,,mxloc,zvsel,nonebloc,xmin-d_dmn,xmax+d_dmn,ymin-d_dmn,ymax+d_dmn,zmin-d_dmn,zmax+d_dmncm,scrap2_v,voluallsvsbv,scrap2_v,scrap1_vC*** MESHesiz,eszvmes,allC*** ELECTRODE VOLTAGEda,electrode1_a,voltda,electrode2_a,volt,VfiniC*** SOLVE/soluallssavesolvfiniC*** POST PROCESS/post1set ! READ RESULTS INTO MADL DATABASEetab,w,sene ! BASED ON ENERGYssum*get,Wnet,ssum,,item,wC1 = 2*Wnet/(V**2)nsel,s,d,volt ! BASED ON CHARGE & VOLTAGEfsum*get,q,fsum,,item,chrgc2 = q/vC_nominal=eps0*(height*width)/separation ! NOMINAL FRINGE FREE VALUE/tla,-0.35,0.90,Capacitance (ANSYS, energy) = %C1% Fd ! ANNOTATION/tla,-0.35,0.85,Capacitance (ANSYS, Q/V) = %C2% Fd/tla,-0.35,0.80,Capacitance (nominal fringe-free) = %C_nominal% Fdalls ! CAPPED SECTION PLOTSwpro,,,90wpof,,,width/2/type,1,7/cpl,1*enddo !指定の値で終わりplns,volt/sho,png $plns,volt $/sho,close $/wait,2plve,ef,,,,vect,,on/sho,png $plve,ef,,,,vect,,on $/sho,close $/wait,2/eof----------------------------------------The capacitance of only the overlapping electrodes can be determined by a theoretical formula, but how should the capacitance be approached taking into account the electric field of the fringes?In this script, the do syntax is turned and parsed using the length of the electrode as a parameter.Best regards, and thank you.Takabayashi -

September 25, 2023 at 3:33 pm

wrbulat

Ansys EmployeeHi Yuuhi,

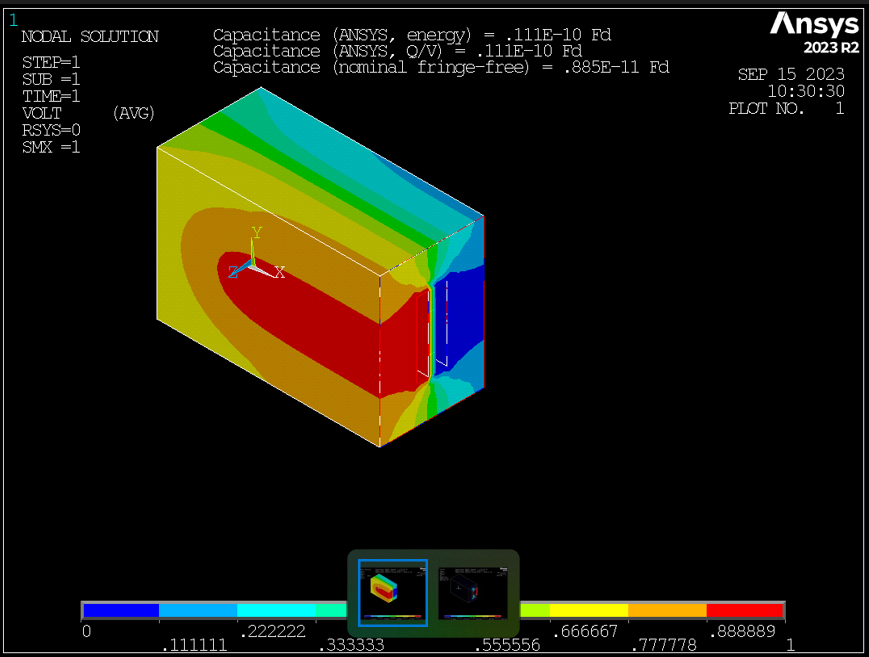

I'm sorry I don't quite understand your question. The input file creates annotated images such as the one below. The first two lines of annotation report the MAPDL-calulated capacitance including fringing deduced from results in two different ways. The third line reports the analytical fringe-free value, which is, as we expect, smaller.

Maybe I'm missing something, but I don't see how you are using loop variable "i" to vary the size or separation of the plates. Are you asking how to vary the geometry in a do loop to investigate the effect of geometry on fringing and capacitance?

Or are you asking for an analytical expression that accounts for field fringing so that you can validate the calculated value from the finite element model? You might have to search the internet for that. I don't think that this article is exactly what you want, but it might help give you an idea what kind of articles you might find if you look further:

(PDF) Effect of Fringing Fields on the Capacitance of Circular Microstrip Disk (researchgate.net)

Kind regards,

Bill

-

September 25, 2023 at 8:10 pm

ty_jpn

SubscriberHi Bill.

Thank you very much for reply.

The effect of the fringe electric field is simulated for each of the given capacitor dimension parameters, with the aim of deriving an approximate analytical expression. (e.g. the respective effects when looping the capacitor width in the do syntax from 0-200).

I understand about the annotations on theoretical values and fringe electric field estimation.

I want to output a list of the results when I loop through the results with the do syntax for this purpose.

Best regards, and thank you.

Takabayashi

-

September 25, 2023 at 8:17 pm

ty_jpn

SubscriberI want to reproduce the article in the URL in MAPDL.

https://ieeexplore.ieee.org/document/9109500/references#references

-

-

-

- The topic ‘Capacitance analysis of parallel plate capacitors in MAPDL’ is closed to new replies.

-

5649

-

1885

-

1404

-

1303

-

1021

© 2026 Copyright ANSYS, Inc. All rights reserved.