-

-

September 17, 2024 at 8:56 am

-

October 2, 2024 at 8:58 pm

HDLI

Ansys EmployeeHello

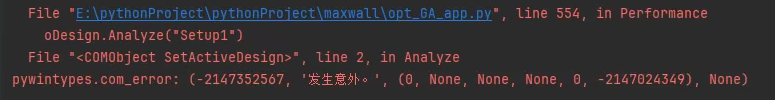

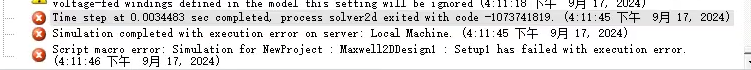

It seems it could not set active design to run setup1. Please debug the coding and submit issue in Github for pyaedt or pyansys questions.

HDLI

-

Viewing 1 reply thread

- You must be logged in to reply to this topic.

Innovation Space

Trending discussions

Top Contributors

-

5664

-

1890

-

1419

-

1304

-

1021

Top Rated Tags

© 2026 Copyright ANSYS, Inc. All rights reserved.

Ansys does not support the usage of unauthorized Ansys software. Please visit www.ansys.com to obtain an official distribution.