-

-

November 28, 2023 at 3:09 am

-

November 30, 2023 at 7:57 pm

Dan Dvorscak

Ansys EmployeeHello Byeonggeon,

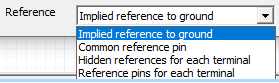

There are very few reasons to use anything other than the implied reference to ground option. Given that s-parameters are a loop inductance model which includes the full return path in each entry, the only reasonable behavior for the reference nodes is to tie them to SPICE node 0, or ground as we often refer to it. The implied reference to ground will save you from having to tie a common reference pin, or indifidual reference pins to ground. I can't remember the last time I've seen a DDR/eye diagram simulation use anything than the implied reference to ground. That optoin is the default for good reason.

Best regards,

-Dan

-

Viewing 1 reply thread

- The topic ‘how to set s-parameter reference import to Designer SI’ is closed to new replies.

Ansys Innovation Space

Trending discussions

- HFSS Incident Plane Wave excitement mode

- Simulation of capacitor combining eddy currents with displacement currents

- How to calculate eddy and hysteresis losses of the core?

- Ansys Maxwell 3D – eddy current

- How to determine initial position in motion setup

- dq graph non-conformity

- How to customize pulse waveform and injection site in microstrip array

- 180 Degree Phase Shift When Measuring S21

- Simplorer+Maxwell Cosimulation results and Maxwell results mismatch

- Parametrizing coil “terminals” with coil geometry

Top Contributors

-

1301

-

591

-

544

-

524

-

366

Top Rated Tags

© 2025 Copyright ANSYS, Inc. All rights reserved.

Ansys does not support the usage of unauthorized Ansys software. Please visit www.ansys.com to obtain an official distribution.