-

-

April 10, 2024 at 7:56 pm

-

April 11, 2024 at 3:31 pm

Guilin Sun

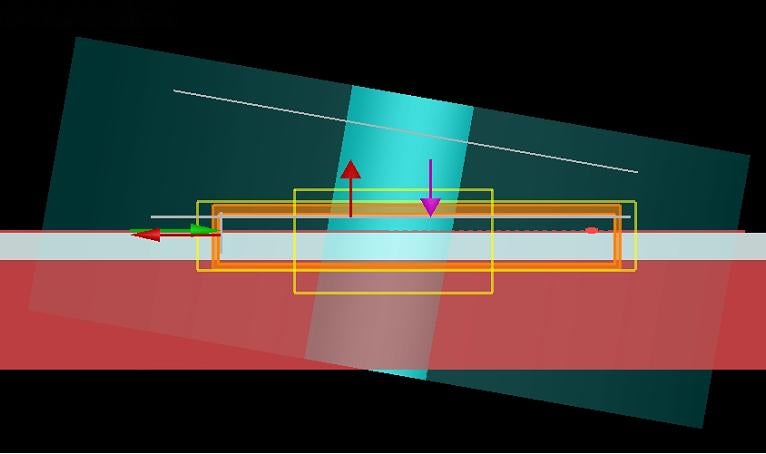

Ansys Employee很自然啊: 光纤在的时候,所用的光源就是光纤模式。没有光纤,Port照样求解了一个模式,因为边界条件是金属,所以你会看到场是均匀的,也可以传播,单结果是错误的,相当于你用平面波来耦合。光纤是该器件的组成部分!

-

April 12, 2024 at 6:00 pm

jiaqing.li

Subscriber哦,哦,好的,谢谢孙老师。

在这个例子中,我同样注意到,因为光纤是贯穿过整个光栅结构的,不知这样的结构布置是否会弱化波导包层厚度对耦合效率的影响?

此外,我还发现,当把包层厚度提高到1.5um后,根据例子中的Port位置计算,Port光源会在包层之内(与实际测量中,光纤位于包层之上,中间夹有一层空气(哪怕很小,但也有一层空气),这样的测量环境相悖),而在官网inverse design grating coupler(2D)的仿真中,干脆取消了包层结构,将整个仿真背景折射率设为二氧化硅;这两个例子均将光源置于包层之中,不知这种与现实测量环境有明显差异的仿真布局,是否会带来比较大的误差?或者说,这样布局的好处是什么?

十分感谢您的耐心解答!

祝好

家青

-

-

April 12, 2024 at 6:57 pm

Guilin Sun

Ansys Employee你可能不清楚当两个物体重叠时结果是什么样,参见:

Ansys Insight: Lumerical 不用布尔运算如何设置嵌套结构 (mesh order)

“当把包层厚度提高到1.5um后" 哪个?SiO2吗?你可以将Port上移啊。

你可能需要学习更多,可以在优酷网上找点视频 https://www.youku.com/profile/index/?uid=UMzc1ODAxMDI4

例子只是演示仿真方法,具体器件你可以设置。

-

Viewing 2 reply threads

- The topic ‘关于光栅耦合器仿真的问题’ is closed to new replies.

Innovation Space

Trending discussions

Top Contributors

-

6034

-

1906

-

1425

-

1308

-

1021

Top Rated Tags

© 2026 Copyright ANSYS, Inc. All rights reserved.

Ansys does not support the usage of unauthorized Ansys software. Please visit www.ansys.com to obtain an official distribution.