-

-

April 15, 2025 at 9:19 am

ee23mtech14014

SubscriberDear Ansys Support Team,

We are students from IIT Hyderabad using Ansys SIwave and EADT for PCB analysis and signal integrity simulations. We are facing the following issues:

Eye Diagram Analysis Issue

While performing eye diagram analysis through the SI Wizard, we provide the correct receiver and driver settings for DIN+, DIN-, L+, and L- (the ports where we want to perform eye analysis).

However, we consistently encounter an error, as there needs to be one driver and one receiver in each net, driver-receiver assistance accordingly, and expose the nets. This is happening despite choosing one receiver and one transmitter on single nets. Multiple options are cooking, and I'm only exposing the relevant ports, but this issue is persistent.

DCIR Drop Test Issue

We imported an ODB++ file of another PCB and attempted to perform a DCIR drop test.

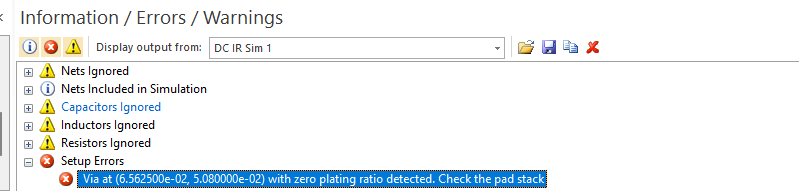

The tool reports a "zero via plating error", pointing to a specific location in the PCB design. However, we have thoroughly checked, and there is no via at that location.

We have validated the via placement multiple times, but the error persists.

Just so you know, these two issues correspond to different printed circuit boards (PCBs).

We would appreciate your guidance in resolving these issues as soon as possible.

-

April 22, 2025 at 8:05 pm

bryan.sandoval

Ansys EmployeeHello,

Eye Diagram:

While you are setting up your Driver/Receivers within the Siwizard in Siwave, you need to make sure to all nets have something assigned to it. If you have extra nets, you may need to remove the unnecessary ports on the nets you are not interested in (this will make sure only the nets you are interested in show up in Siwizard). Typically, in those types of errors messages, it tells you exact what nets needs to be assigned an IBIS model. Double check and make sure that you have a driver/receiver assigned to that net. Exposing/unexposing nets only exposes the pin on the s-parameter model when it is created/used in Circuit. It does not hide/remove the pin from being solved.

Also, make sure that everything that is set as a "Receiver" as the

Type assigned to it, then is has an appropriate "Driver" on the other side. For example, if you have a list of nets that start at U1 and then ends at J1 (and all the nets at the J1 side is set to "Receiver" type), then make sure that those same nets at the U1 side is set as a driver.DCIR Drop Test Issue:

Sometimes the Siwave does not exactly show you the exact location of the via placement. Is there any vias around that has zero-plating defined within it's padstack properties? Siwave not showing the exact location of the via might be a defect of the tool, but it is hard to confirm without having the project.

Here are my suggestions:

- First, try to identify if that one particular via is important to the simulation. Cross reference is with you PCB board in another ECAD viewer. Since the simulation finishes, it may not be a big deal if it is not relevant to the area you are checking for DCIR.

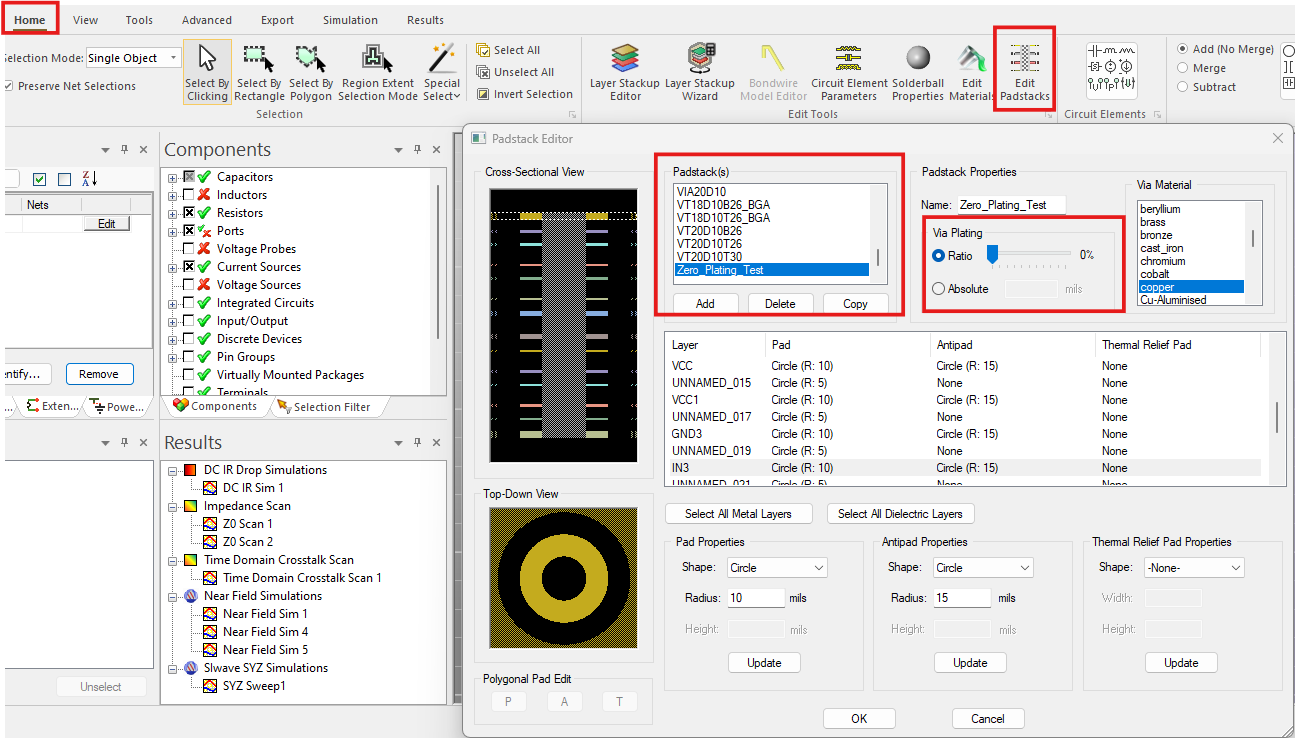

- Secondly, Verify that all your padstack definitions are correctly defined for you vias. You can check padstacks by doing to the "Home" tab and then select the "Edit Padstacks" button. This will open up the padstacks and you will need to go through each padstack to find out which one has zero-plating define and change it. See image below

Regards,

Ansys Technical Support

-

- You must be logged in to reply to this topic.

- Three-Phase Voltage Imbalances in dual stator electric generator

- Co-simulation in Q3D, Icepak – meshing problem

- Classic Icepak – clarifications on Boundary condition

- Link the Circuit to 3D Terminals

- Magnetic Dipole moment calculation

- Integration lines or U Axis Line for circular and rectangular ports

- Core Loss in ANSYS MAXWELL Eddy Current solution

- exporting and importing my Netlist for my external circuit

- Error of Metal Fraction in Icepak Classic.

- The unit of theta in Is*sin(2*pi*fre*Time+theta-2*pi/3)

-

4597

-

1495

-

1386

-

1209

-

1021

© 2025 Copyright ANSYS, Inc. All rights reserved.