TAGGED: AEDT-ICEPAK

-

-

November 7, 2024 at 3:30 am

weilun.ang

SubscriberHi guys,

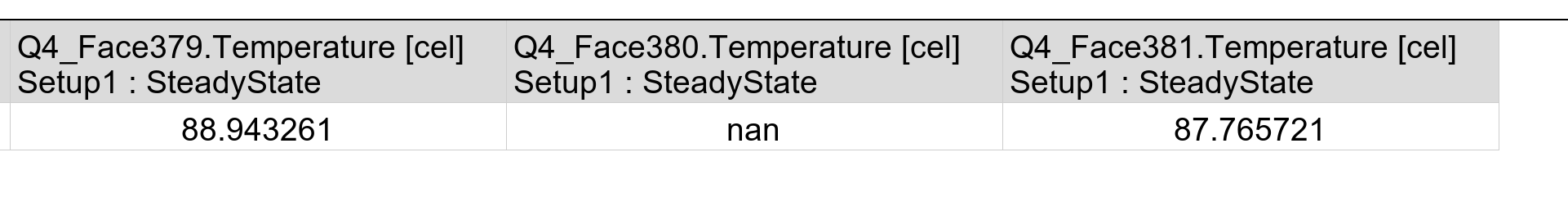

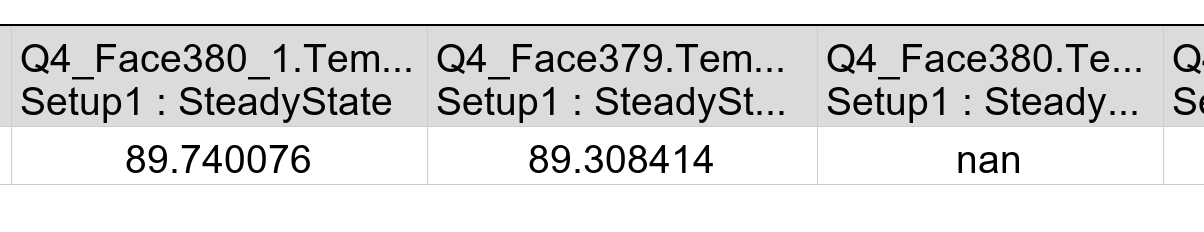

I am currently running some simulations in AEDT Icepak to determine how good the heat transfer is of a MOSFET into the PCB. For this I have setup a few monitors, one of them is on the top case, and one of them is on the bottom face (face between MOSFET and PCB). When I view the results, the monitor on the bottom face is returning a NaN value. What is the issue here?

Thanks in advance! -

November 8, 2024 at 3:20 pm

Iceman

Ansys EmployeeIs the MOSFET modeled as network? If so, the monitor might have been put inside the network object due to numerical rounding error. Since Solve Inside is unchecked for network objects, there won't value for monitor. Please shift the monitor point slightly downward, then you should see result. Thanks. -

November 8, 2024 at 5:32 pm

weilun.ang

SubscriberIt is currently only being modeled as a block thermal and not a network, but I will double check if the solve inside is enabled. Is there anything else that might be causing this issue?

-

November 8, 2024 at 5:39 pm

Iceman

Ansys EmployeeIf there is mesh where the monitor is located, there should be results. Please check the mesh. Thanks.

-

November 8, 2024 at 7:56 pm

-

November 8, 2024 at 8:07 pm

Iceman

Ansys EmployeePlease check the object priority of MOSFET and PCB. If the surface monitor is assigned on the face of object with lower priority, there won't be results as the mesh will belong to the object with higher priority in overlapped region. Please use mesh viewer to check the mesh on the face with surface monitor assignment. If this is the issue, please make the MOSFET priority higher than that of PCB. Thanks.

-

November 8, 2024 at 11:01 pm

weilun.ang

SubscriberThe meshing priority was the issue. Thanks!

-

November 8, 2024 at 11:03 pm

Iceman

Ansys EmployeeYou are welcome

-

-

-

- You must be logged in to reply to this topic.

-

5709

-

1906

-

1419

-

1305

-

1021

© 2026 Copyright ANSYS, Inc. All rights reserved.