TAGGED: ansys-electronics-desktop, circuits

-

-

January 24, 2024 at 2:25 pm

lkammann

SubscriberHi everyone, I'm trying to perform some transient simulations for a rank of DDR3L SDRAMs on a PCB, but the simulation keeps failing because it requires more RAM (I have 64GB DDR4 RAM on my computer). Trying to see if I could make any changes in the simulation settings to make it less memory-consuming, I saw there is an option to enable a convolution-solving method. When I used it, it took much more time (about 24 hours of simulation) but it handled to do it without running out of memory.

I want to have a better understanding of the implications of using either the default solving method (which I believe uses state space) or the convolution-solving method. Are they equivalent in terms of results accuracy? Why do they require different memory and time to solve?

-

January 29, 2024 at 8:56 pm

Dan Dvorscak

Ansys EmployeeHello Lucas,

In general we consider convolution to be a less robust, and generally less accurate algorithm. I can't get into the details of the alorithms here, but state-space is strognly preffered with convolution provided basically as a fall back.

On that note 64GB of memory is usually more than enough for a DDR Circuit transient. Can you let me know what is going on when it runs out of memory? Is it at the start of the transient simulation? That is when we do the actaul state-space fitting, and is usually the most memory intensive part of the solve. Did you happen to enforce passivity on the s-parameters, and if so which option did you choose?

Best regads,

-Dan

-

January 30, 2024 at 11:10 am

lkammann

SubscriberHi Dan, thanks for your reply.

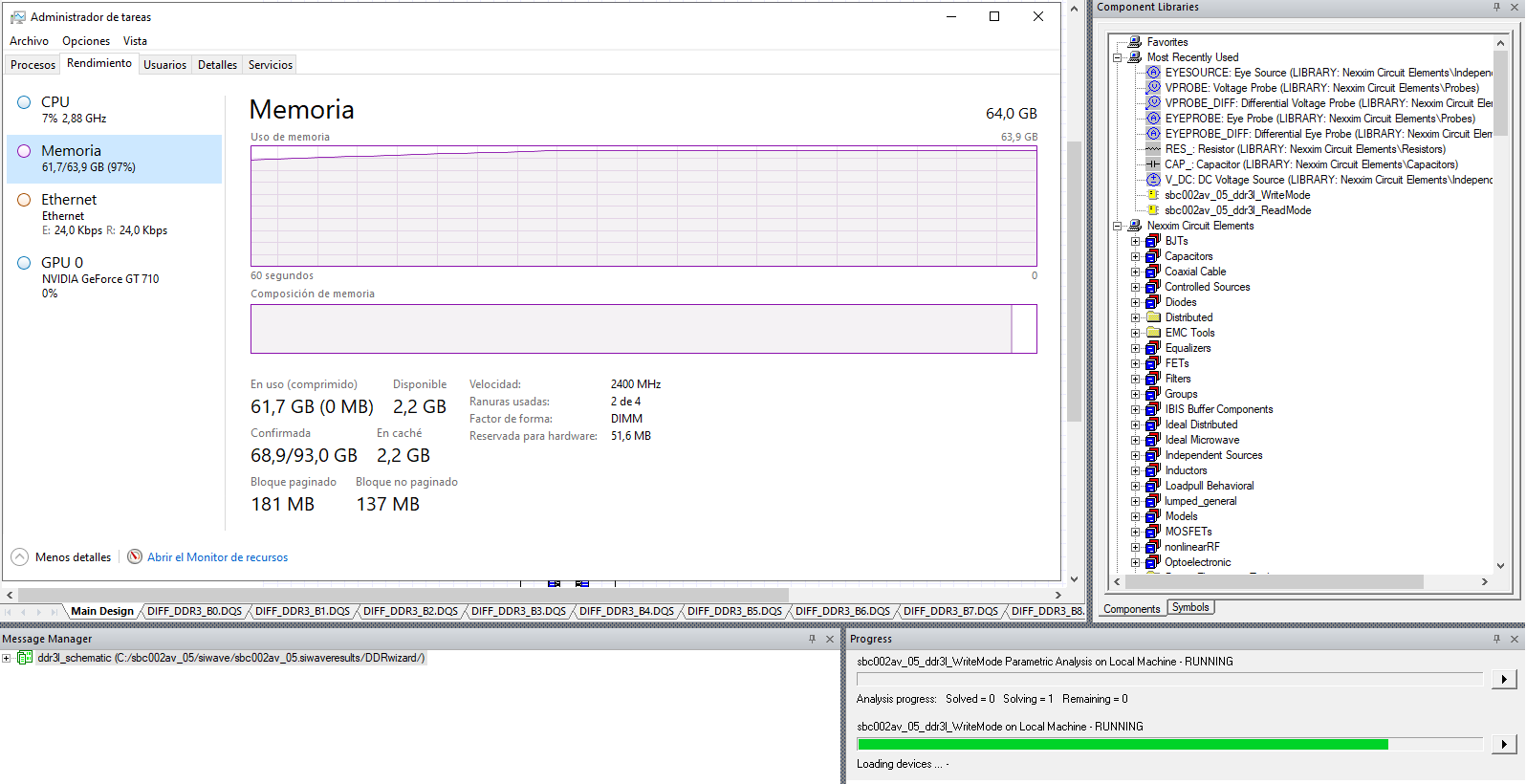

The simulation fails in the “Loading devices…” stage, I believe it’s when it performs the state-space fitting as you say. It throws an error that says “memory allocation error”. I monitored the process with the Resources Monitor for Windows and it consumes over 100% of the available memory until it fails. I disabled the passivity enforcement in the DDRwizard because I read that it tends to use much more memory. The following image show the memory consumption:

Our design has 9 DDR3L SDRAMs operating at 1866Mbps. I need to analyze the compliance of the design with the JEDEC standard. So I extracted the S-parameters using the DDRwizard for the data buses of all the SDRAMs and the control signals (address, command, clock, etc). Then, I performed a transient simulation with the circuit created by the wizard to extract the waveforms so I could use the Compliance Toolkit to evaluate the compliance. The simulation fails because it runs out of memory when using the state-space representation, but it works with the convolution method. I compared both solutions when running it for only a single DDR3L SDRAM, and the results difference was negligible. Although the convolution method takes much more time to finish.

What do you think? I’d say that maybe there’s not much difference in the results obtained using the convolution method, and the only drawback in my particular case would be the simulation time (which is more or less 48 hours for the 9 SDRAMs).

Any advise is welcomed.

Thanks in advance.

-

January 30, 2024 at 2:29 pm

Dan Dvorscak

Ansys EmployeeYes, it is doing state-space fitting when it runs out of memory. Can you check to see if passivity enforcement is set in the s-parameter component in the Circuit schematic? To do this, right moust click on the component, select "Edit Model", and then check the passivity option in the Options tab.

If that option is set to convex optimization instead of IFPV, that could explain the large memory usage here. Note this is separate from passivity enfrocement being applied during the SYZ sweep in SIwave. -

February 1, 2024 at 6:20 pm

lkammann

SubscriberThese are some screenshots of the "Edit Model" option and the "Simulation Options". With this, I was able to run the time-domain simulation using the Convolution Method without Passivity Enforcement in only 27 hours with not more than 16GB of RAM. Would you suggest using another set of settings to perform a less memory-consuming simulation with the state-space representation? I tried this very same simulation by disabling the option "Use Convolution for S Elements", and it ran out of memory.

Is anything of this optimized in the 2024 version of Ansys Electronics Desktop? I believe that my license allows me to update the version of Ansys (I'm currently working with the 2023 version), and maybe there are bugs solved or further optimizations for the solver.

-

February 1, 2024 at 6:31 pm

Dan Dvorscak

Ansys EmployeeI would try turning off that "use convolution for s-elements" option, and in the s-parameter setup form set the method to "state-space" and passivity enforcement option to "IFPV". Just to ensure that it isn't falling back to a more memory intensive algoritm. Can you try that and let me know if it works?

-

February 5, 2024 at 12:43 pm

lkammann

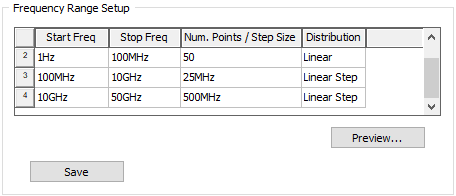

SubscriberI tried your proposed configuration, but it failed again. Just for completeness, here is a screenshot of the error message thrown by Ansys Electronics Desktop:

The error says "memory allocation failed". This only happens when I use the state-space representation to solve the transient simulation. I've tried forcing the use of IFPV, but it made no difference. I have tried a lot of different things, looks like I reached a dead-end.

-

February 5, 2024 at 2:42 pm

Dan Dvorscak

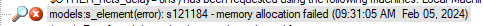

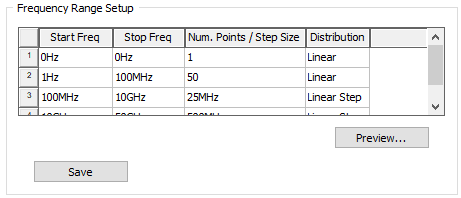

Ansys EmployeeYes, it really looks to be running out of memory with state-space and IFPV. Can you tell me any more about the model? How many ports? What is the frequency sweep info?

-

-

February 5, 2024 at 3:06 pm

lkammann

Subscriber-

February 5, 2024 at 3:41 pm

Dan Dvorscak

Ansys EmployeeOK, 450 ports is a lot. In order to run this in state-space, which is typically much faster that convolutoin, you may just need a maching with more memory to get that fit done.

It may not help with the memory usage, but I'm not sure I like that frequency sweep. I usually recommend doing two separate sweeps. Frist a linear sweep betwen 0Hz and your top frequency (in this case 50MHz) in 10MHz steps. And then a log sweep from 1Hz to 10MHz with 10 points per decade.

Again, I'm not sure it well help with memory, but your original sweep has a couple of issues. The big one is the 500MHz steps at high frequency. That kind of extreme undersampling almost always makes the s-parameters numberically non-causal. And that can cause all kinds of downstream problems.

-

-

- The topic ‘Ansys Electronics Desktop – Circuits – Convolution for transient simulation’ is closed to new replies.

-

5649

-

1885

-

1404

-

1303

-

1021

© 2026 Copyright ANSYS, Inc. All rights reserved.