TAGGED: ansys-electronics-desktop, Ansys-Siwave, siwave, toolkit

-

-

February 2, 2024 at 11:33 am

lkammann

SubscriberHi, I'm trying to validate the design of a board's memory system. The system contains 9 DDR3L SDRAMs of 8 bits each one (64 bits + 8 ECC bits), running at 1866Mbps. I'm using Ansys SIwave to extract the board's S-parameters with the DDRwizard, and afterward, I'm using the automatically generated schematics in Ansys Electronics Desktop to perform a transient simulation and use the waveform results to run the Compliance Toolkit for DDR3L that provides Ansys.

What I want to do is generate a JEDEC compliance report to verify the design, and I understand that this Toolkit provides the means to automatically perform that analysis and export the report. After the simulation finished, I ran the Compliance Toolkit for DDR3L, assigned the signals (DQ, DQS, DM, ADDRESS, CLOCK), set everything up, and selected the reports. But when I try to "Run" the "Waveforms" report that checks the setup and hold times, it crashes and closes.

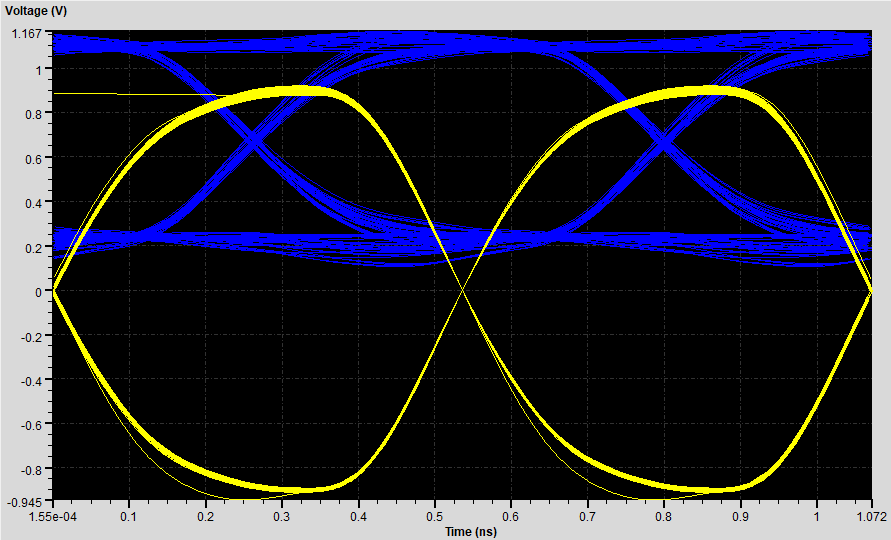

I managed to debug that the problem is the DQ/DQS signals, as running it only with the address signals doesn't fail. The simulation is for the Write Mode, and the total simulated time is 70 ns. The EyeDiagram report works fine, and this is a screenshot of it for the DQ0 bit using the DQS signal as a reference.

I've been having lots of trouble trying to generate a decent JEDEC compliance report automatically with Ansys, am I using the correct tools? Are we supposed to run the DDRwizard, run the transient simulation, and use the Compliance Toolkit? Why can this be crashing?

Thanks in advance. -

February 2, 2024 at 2:51 pm

Dan Dvorscak

Ansys EmployeeUnfortunately, the DDR Virtual Complaince Toolkits were recently retired from AEDT as they are no longer being actively developed. We are evaluating replacement solutions, but those are still in the works.

Becase of this, it is very hard to say why it would be crashing. You mentions that the toolkit crashes when you run the full set of nets, but runs when using just the address signals. What happens if you try just the DQ or just the DQS nets?

-

February 2, 2024 at 4:21 pm

lkammann

SubscriberSo, you're telling me that Ansys currently does not provide the means to perform a complete compliance report and verification for DDR interfaces.

-

February 2, 2024 at 4:48 pm

Dan Dvorscak

Ansys EmployeeNot in the current release of AEDT, no.

-

- The topic ‘Ansys DDR3L Compliance Toolkit Crashes’ is closed to new replies.

-

5824

-

1906

-

1420

-

1305

-

1021

© 2026 Copyright ANSYS, Inc. All rights reserved.