TAGGED: grating, subwavelength

-

-

April 7, 2023 at 8:10 am

Liu dazhuo

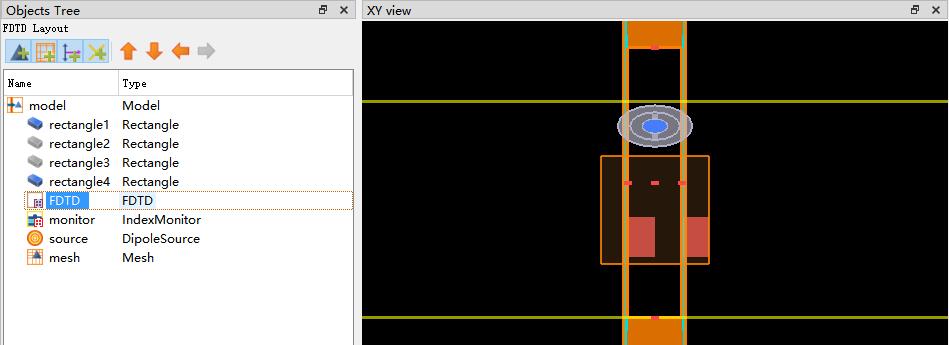

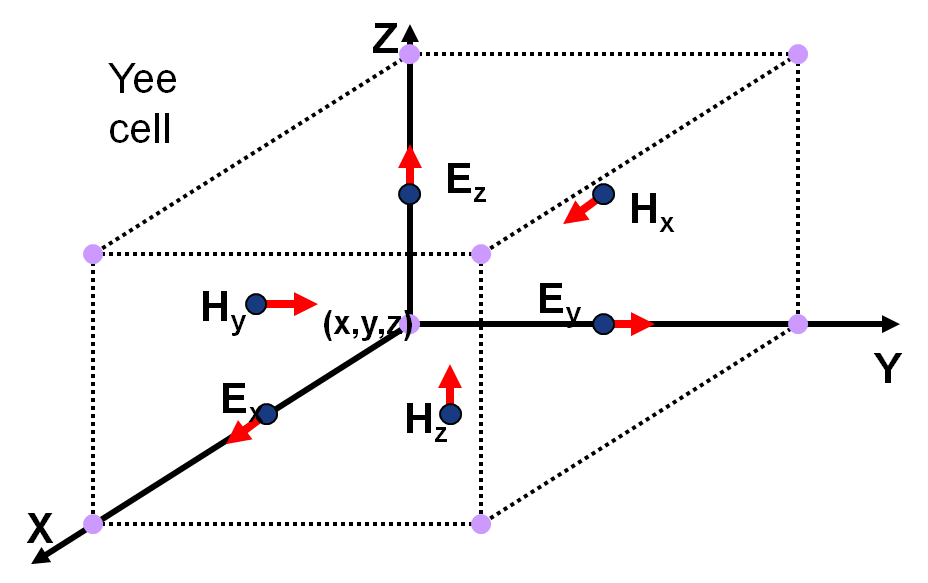

Subscriber图1为仿真的示意图

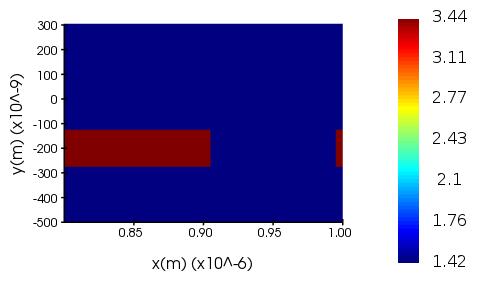

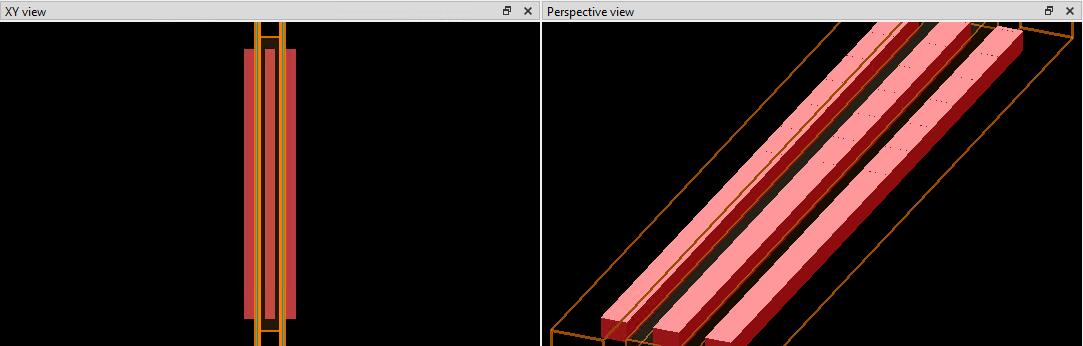

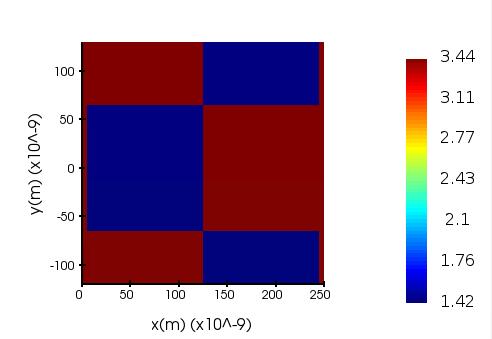

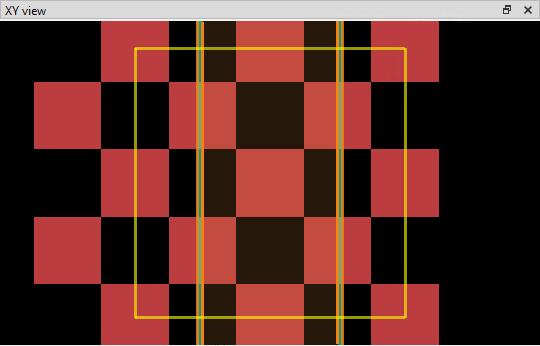

x方向使用 Bloch BC,y,z方向使用 PML BC,因为是仿真光栅结构,仿真区域的 x span 就是光栅的周期,光栅的占空比为 50%,我选择把光栅的边界与仿真区域的内边界重叠,这样就需要在左右两边画出额外的周期单元填充边界区域,因此我画出了两个光栅。经过仿真,发现把光栅单元放在仿真区域的中心和使用这种设置的仿真结果不一样,于是我添加了一个Index Monitor查看折射率分布,如图2所示

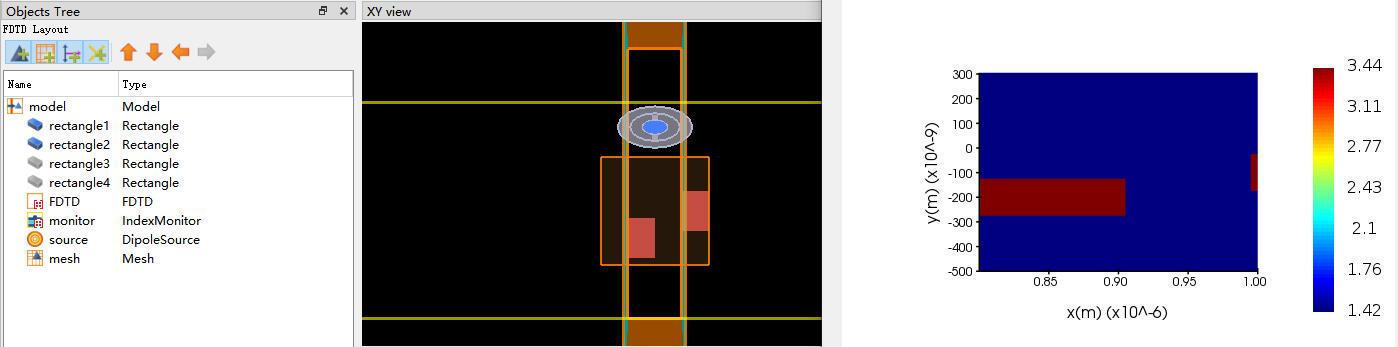

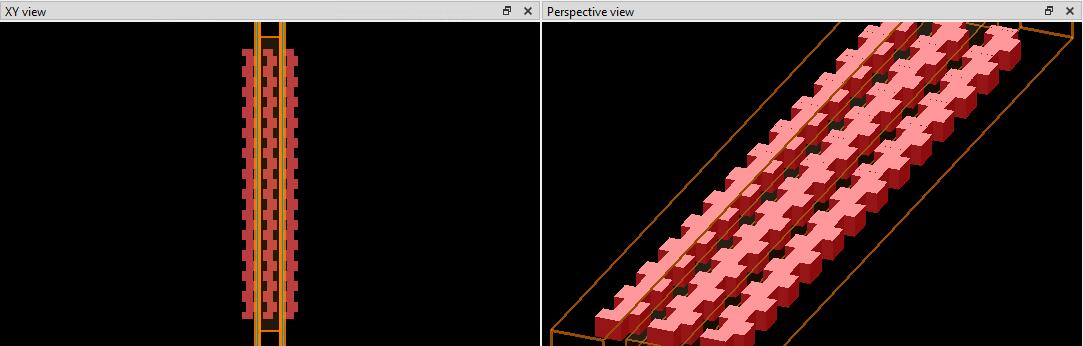

可以看到,右边光栅与Bloch BC内边界重叠的位置向仿真区域内突出了一小段。接着,我把右边的光栅单元向上平移了一小段,如图3所示

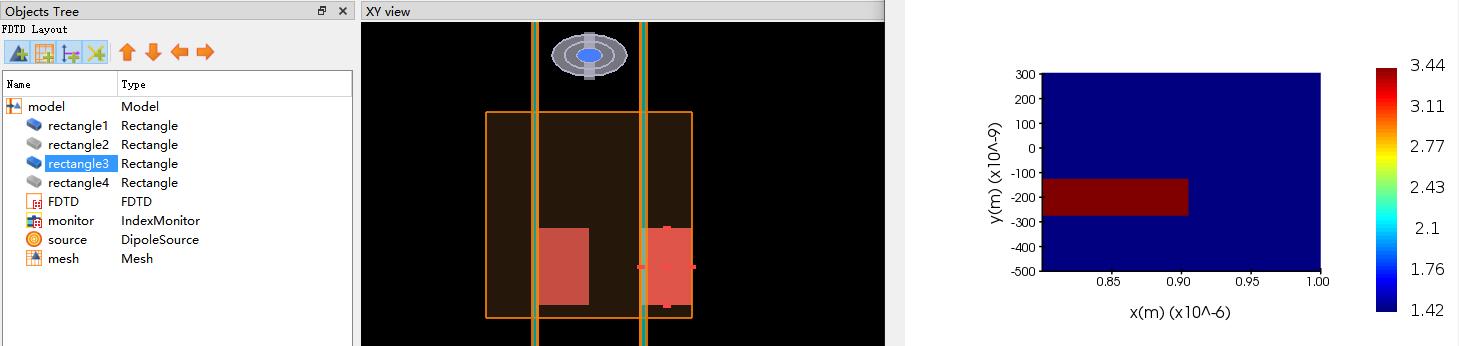

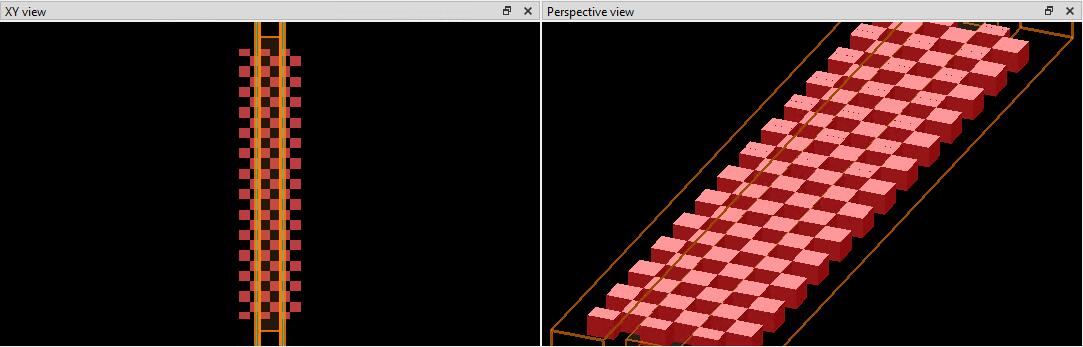

通过Index Monitor查看的折射率分布,可以看到,右边突出的折射率块也相应上移。最后,我又重新添加了一个与图1右边光栅属性完全一致的光栅,如图4所示

奇怪的是,这次在右边的边界处并没有向内突出一块

-

April 10, 2023 at 6:31 pm

-

April 11, 2023 at 7:31 am

Liu dazhuo

Subscriber老师您好,我想仿的是在传统 SWG 向 Bricked-SWG 过渡的过程中,有效折射率的变化,如图1至图3所示

可以看到,在光栅上的小段完全错开(图3)时,物体的边界将不可避免地与 Bloch BC 重合,此时 Index Monitor 查看的折射率分布如图4所示

因此我仿真得到的有效折射率与原论文相比高了0.03,这会对计算拍长影响显著。与此同时,我也尝试了将物体沿x方向平移了一段距离,如图5所示,这样不会出现物体边界和 BLoch BC 重合的问题,但是,这两种方法得到的结果相差不大,却都比原论文的结果高。(Ps. 我使用同样的 dipole cloud, bandstructure,仿真区域以及精度仿得的传统 SWG 和原论文几乎完全相同)

原论文链接:https://onlinelibrary.wiley.com/doi/full/10.1002/lpor.202000478

题目:Bricked Subwavelength Gratings: A Tailorable On-Chip Metamaterial Topology

-

April 11, 2023 at 7:48 am

Liu dazhuo

SubscriberPs. 传统 SWG 的仿真是将光栅放在仿真区域中心的,如果将光栅边界与 Bloch BC 重合的话得到的结果也和原论文不一样。

in addition,将光栅的小段错开一点并将光栅放在仿真区域中心(不与 Bloch BC 重合)的仿真结果也和原论文不同。

mesh大小和原论文使用的一致(在x,y,z方向均为10nm),但是通过 Index Monitor 查看光栅的宽度总会宽 5nm 或者窄 5nm

-

-

- The topic ‘仿真光栅时遇到光栅边界与仿真区域边界重合的问题’ is closed to new replies.

-

5884

-

1906

-

1420

-

1306

-

1021

© 2026 Copyright ANSYS, Inc. All rights reserved.